Agilent E2925B Opt. 320 C-API/PPR

**Programmer's Guide**

#### **Important Notice**

This document contains propriety information that is protected by copyright. All rights are reserved. Neither the documentation nor software may be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine-readable form, in whole or in part, without the prior written consent of Agilent Technologies.

© Copyright 2000 by: Agilent Technologies Herrenberger Straße 130 D-71034 Böblingen Germany

The information in this manual is subject to change without notice. Agilent Technologies makes no warranty of any kind with regard to this manual, including but not limited to the implied warranties of merchantability and fitness for a particular purpose.

Agilent Technologies shall not be liable for errors contained herein or direct, indirect, special, incidental, or consequential damages in connection with the furnishing, performance, or use of this manual.

Brand or product names are trademarks or registered trademarks of their respective companies or organizations.

Author: Anja Schauer, t3 medien GmbH

# Index

| About This Guide     |                                                   |    |

|----------------------|---------------------------------------------------|----|

| Documentation C      | )verview                                          | g  |

| Programming Overview |                                                   | 11 |

|                      | Programming Interfaces                            | 12 |

|                      | C Programming Libraries                           | 13 |

|                      | Generic C-API Functionality                       | 14 |

|                      | Protocol Permutation and Randomizer Functionality | 15 |

|                      | Contributions of the PCI PPR Software             | 17 |

|                      | Benefits                                          | 18 |

|                      | Error Checking                                    | 20 |

|                      | Example: Using the C-API                          | 22 |

|                      | Example: Using the PPR                            | 23 |

| Programming the      | : Framework                                       | 27 |

|                      | Connection and Initialization                     | 28 |

|                      | Functions Overview                                | 29 |

|                      | Examples                                          | 30 |

|                      | Administration                                    | 33 |

|                      | Functions Overview                                | 35 |

|                      | Examples                                          | 36 |

|                      | Power-Up and Reset Control                        | 37 |

|                      | Functions Overview                                | 39 |

|                      | Examples                                          | 40 |

|                      | Card Status Register Access                       | 42 |

|                      | Functions Overview                                | 42 |

|                      | Example                                           | 43 |

| Programming the Analyzer              |                  |  |

|---------------------------------------|------------------|--|

| Protocol Observer Programming         | 47               |  |

| Functions Overview                    | 48               |  |

| Example                               | 48               |  |

| Timing Check Programming              | 49               |  |

| Functions Overview                    | 50               |  |

| Example                               | 51               |  |

| Programming the Pattern Terms         | 52               |  |

| Functions Overview                    | 53               |  |

| Example                               | 54               |  |

| Sequencer Programming                 | 55               |  |

| Functions Overview                    | 58               |  |

| Example                               | 60               |  |

| Performance Measurement Programm      | ning 64          |  |

| Functions Overview                    | 65               |  |

| Example                               | 67               |  |

| Trace Memory Programming              | 70               |  |

| Functions Overview                    | 72               |  |

| Example                               | 73               |  |

| Programming the Exerciser             |                  |  |

| Reading from and Writing to the Memo  | ories 77         |  |

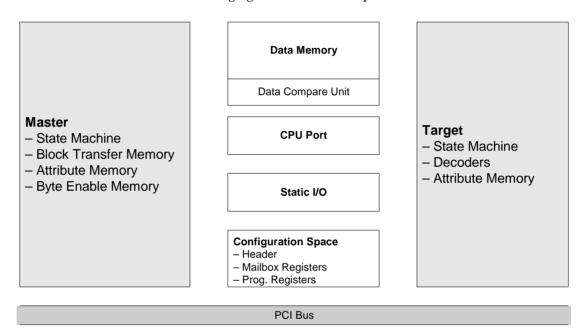

| Exerciser Block Diagram               | 78               |  |

| Programming the Exerciser as a Maste  | er Device 80     |  |

| Programming Generic Master Properties |                  |  |

| Master Block Transfer Memory Program  |                  |  |

| Master Attribute Memory Programming   | 89               |  |

| Master Attribute Group Programming    | 95               |  |

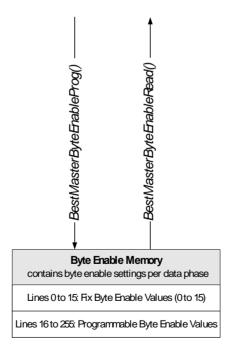

| Byte Enable Memory Programming        | 101              |  |

| Master Run                            | 103              |  |

| Programming the Exerciser as a Targe  | t Device 105     |  |

| Target Operation                      | 105              |  |

| Programming Generic Target Properties | 107              |  |

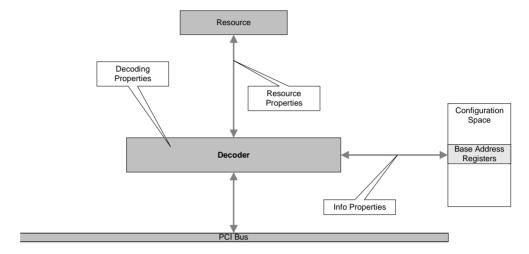

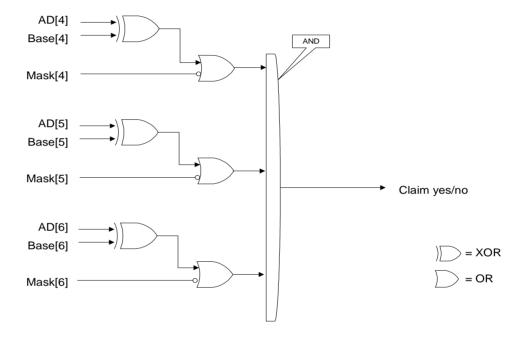

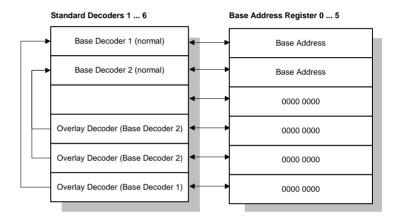

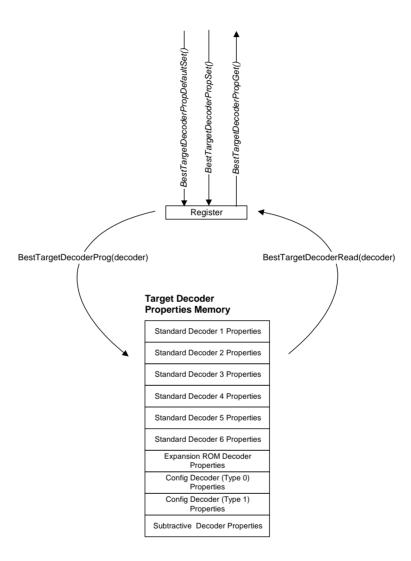

| Programming the Target Decoder Prope  | rties Memory 109 |  |

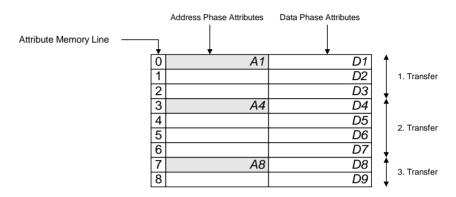

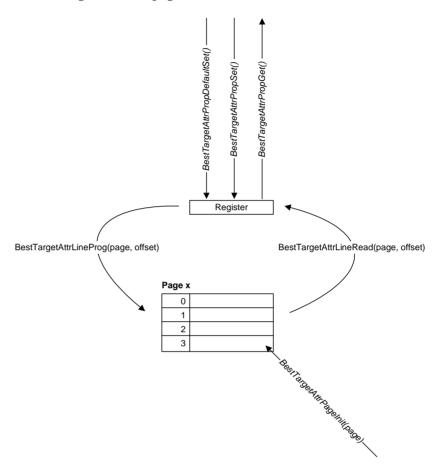

| Target Attribute Memory Programming   | 123              |  |

| Target Attribute Groups Programming   | 129              |  |

|                            | Target Run                                                                 | 135               |

|----------------------------|----------------------------------------------------------------------------|-------------------|

|                            | Configuration Space Header Programming                                     | 136               |

|                            | Expansion ROM Programming                                                  | 141               |

|                            | Data Memory and Compare Unit Programming                                   | 142               |

|                            | Functions Overview                                                         | 142               |

|                            | Example                                                                    | 143               |

|                            | Host Access Programming                                                    | 144               |

|                            | Functions Overview                                                         | 144               |

|                            | Example                                                                    | 145               |

|                            | Interrupt Programming                                                      | 146               |

|                            | Example                                                                    | 146               |

|                            | Built-In Test Programming                                                  | 147               |

|                            | Functions Overview                                                         | 148               |

|                            | Example                                                                    | 149               |

| Programming the Interfaces |                                                                            |                   |

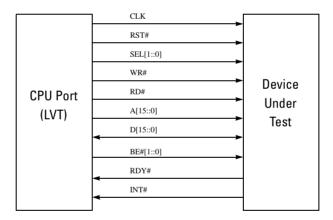

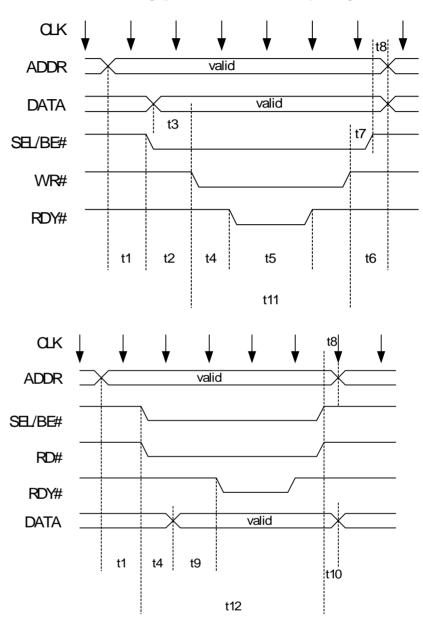

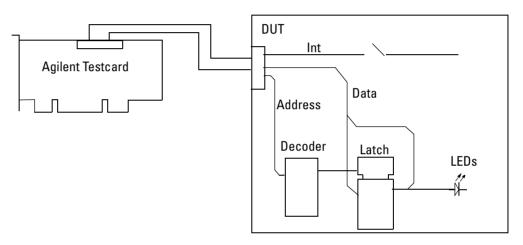

|                            | CPU Port Programming                                                       | 152               |

|                            | Functions Overview                                                         | 157               |

|                            | Example                                                                    | 159               |

|                            | Static I/O Port Programming                                                | 160               |

|                            | Functions Overview                                                         | 162               |

|                            | Example                                                                    | 162               |

|                            | Trigger I/O Sequencer Programming                                          | 163               |

|                            | Functions Overview                                                         | 164               |

|                            | Example                                                                    | 165               |

|                            | Example                                                                    |                   |

|                            | LED Controlling and Display Functions Overview                             | 169               |

|                            | •                                                                          |                   |

|                            | LED Controlling and Display Functions Overview                             | 169               |

|                            | LED Controlling and Display Functions Overview Example                     | 169<br>169        |

|                            | LED Controlling and Display Functions Overview Example Mailbox Programming | 169<br>169<br>171 |

| Using the PPR |                                                         | 177 |

|---------------|---------------------------------------------------------|-----|

|               | Generating Permutations                                 | 178 |

|               | How to Write a Test Program                             | 182 |

|               | Example Test Design                                     | 183 |

|               | PPR Administration                                      | 186 |

|               | Functions Overview                                      | 187 |

|               | Example                                                 | 188 |

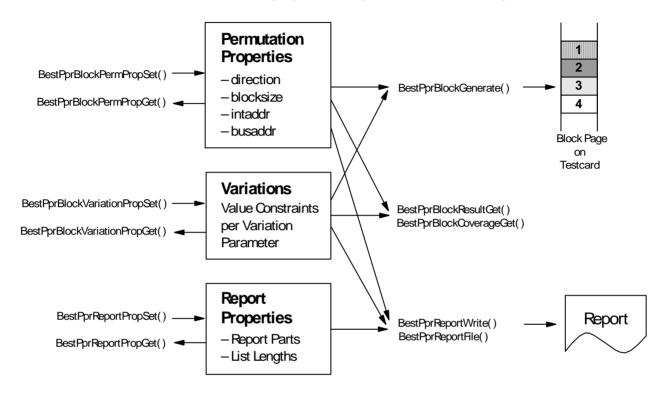

|               | Programming Master Block Permutations                   | 189 |

|               | Functions Overview                                      | 195 |

|               | Example                                                 | 196 |

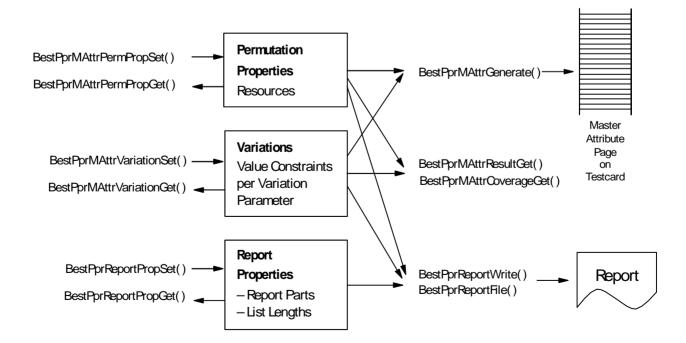

|               | Programming Master Attribute Permutations               | 199 |

|               | Functions Overview                                      | 201 |

|               | Example                                                 | 203 |

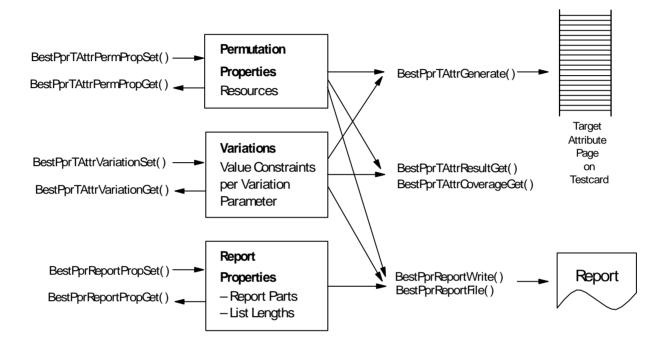

|               | Programming Target Attribute Permutations               | 205 |

|               | Functions Overview                                      | 207 |

|               | Example                                                 | 208 |

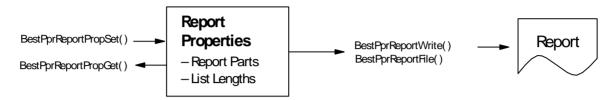

|               | Generating PPR Reports                                  | 209 |

|               | Functions Overview                                      | 210 |

|               | Example                                                 | 210 |

|               | Running the PPR Test                                    | 211 |

|               | Example                                                 | 212 |

|               | Analyzing the Report                                    | 213 |

|               | Report Header                                           | 213 |

|               | Report of Block Permutations                            | 214 |

|               | Report of Master Attribute Permutation                  | 221 |

|               | Report of Master Block vs. Master Attribute Permutation | 226 |

|               | Report of Report Properties                             | 227 |

|               | Block Page Contents                                     | 228 |

Further Options and Possibilities

**Report Listing**

229

232

# **About This Guide**

#### **Programming Interface**

The Agilent E2925B testcard is used for testing PCI chips, cards and systems. For this purpose, the testcard allows you to develop test programs by using:

- C-Application Programming Interface (C-API)

The C-API allows you programmable control for the whole system and allows you the integration into existing test environments.

- Additional functions performed by the PCI Permutator and Randomizer software (PPR)

These functions allow you to prepare and perform systematic functional tests at the protocol level, especially exposing PCI devices of a computer system to variable stressful PCI traffic.

#### **Programmer's Guide Structure**

For developing C programs or for using the command line interface of the graphical user interface, this Programmer's Guide gives you good background knowledge of the programming models for the Agilent E2925B testcard.

The programmer's guide contains the following chapters:

- "Programming Overview" on page 11 gives basic information about writing C programs, such as where to find the required libraries, compilation and error checking.

- It also provides two examples, one for using the C-API and one for using additional PPR functions.

- "Programming the Framework" on page 27 provides information about the first steps to be performed in any C program, such as the testcard's connection to a control PC and its initialization.

- "Programming the Analyzer" on page 45 provides information about programming models for all tasks of PCI analysis to monitor the PCI bus, to detect specific events, to measure and to evaluate the occurrences of signals on the bus.

- "Programming the Exerciser" on page 75 provides information about

the programming models for programming the testcard as a master

and as a target device and for resources shared by both, such as data

memory and compare unit.

#### **About This Guide**

- "Programming the Interfaces" on page 151 provides information about the programming models for the available application interfaces, such as CPU port, static I/O port, trigger I/O sequencer, LED display and mailbox.

- "Using the PPR" on page 177 provides an overview of the features of the software, and shows how a test program is designed and implemented.

# **Documentation Overview**

This section shows you the different types of documents offered by Agilent Technologies and gives you an overview of which documents are available when you work with the Agilent E2925B PCI Exerciser and Analyzer.

The following documents are available:

#### **User's Guides**

#### • Agilent E2925B Opt. 300 PCI Exerciser User's Guide

Provides information on programming the testcard as an master and/or target device. It shows you how to actively stimulate the PCI bus.

#### • Agilent E2925B PCI Analyzer User's Guide

Provides information on how to examine the behavior of a PCI device on the bus and shows how to perform functional tests such as data compares.

#### Agilent E2925B Opt. 200 PCI Performance Optimizer User's Guide

Provides information on how to evaluate and optimize any device under test in terms of the performance. It shows how performance measures as efficiency, data throughput, or bus utilization, allow you to compare and communicate the test results.

#### • Agilent E2925B Opt. 320 C-API/PPR Programmer's Guide

Provides information on how to set up test programs using the C functions described in the corresponding C-API/PPR Reference.

#### **GUI and C-API/PPR References**

#### • Agilent E2925B Windows and Dialog Boxes Reference

Provides reference information on all windows and dialog boxes of the Agilent E2920 graphical user interface (GUI).

#### Agilent E2925B Opt. 320 C-API/PPR Reference

Describes all C functions, types and definitions of the application programming interface and the PPR software of the Agilent E2925B PCI testcard.

This reference also provides the commands and abbreviations that are used in the command line interface (CLI) of the GUI.

#### **Documentation Overview**

# **Programming Overview**

The following sections give basic information about the C-API and the PPR software:

- The ways in programming the testcard are shown in "Programming Interfaces" on page 12.

- Where to find the libraries, what you must do when writing C programs and how to compile the programs depending on the operating system, can be found in "C Programming Libraries" on page 13.

- The features of the C-API and the PPR software can be found in "Generic C-API Functionality" on page 14 and "Protocol Permutation and Randomizer Functionality" on page 15.

- Error handling macros, which are needed to return error codes of C functions, are explained in "Error Checking" on page 20.

- Two example C programs show you how to use the C-API and the PPR software. See "Example: Using the C-API" on page 22 and "Example: Using the PPR" on page 23.

# **Programming Interfaces**

The testcard can be programmed in the following ways:

• By writing C programs

The testcard is shipped with an application programming interface for the C programming language.

See "C Programming Libraries" on page 13.

• By using the command line interface (CLI)

The CLI provides an easy-to-use graphical user interface for entering commands. Descriptions of the CLI commands can be found in *Agilent E2925B Opt. 320 C-API/PPR Reference*, together with their corresponding C function.

For more information, refer to "Using the Command Line Interface" in the Agilent E2925B Opt. 300 PCI Exerciser User's Guide.

Hints for programming on 64 bit systems

If you plan to run the PCI software under 64 bit Itanium systems, you should read the following.

Targeted are currently the 64 bit Microsoft .NET Server OSes.

To install, you need a separate installation file, named setup64.exe, located in the CD's ia64 directory. Do not install the 32bit setup.exe.

On 64bit Itanium systems the following is true:

· Kernel mode:

Drivers always need to be 64 bit drivers; 32 bit drivers wont work. Especially, this means that you can't use the existing 32 bit drivers. Our 64 bit drivers are named b\_2kpci\_64.sys, b\_2khif\_64.sys, b\_usb\_64.sys and b\_usbgen\_64.sys.

• User mode:

If you are starting an application, the .exe (and all needed dlls) need to be either all 32 bit files or all need to be 64 bit files, i.e. you cannot mix them. For example a 64 bit .exe cannot use a 32 bit dll.

Our 64-bit dlls always have the suffix "xp64", e.g. capixp64.dll (instead of capikk.dll in 32 bit mode).

• The PCI GUI always only runs in 32bit mode (so they alway needs the corresponding 32 bit dlls).

If you want to write your own C-API programs, you can use the provided 64bit dlls though and run your program as 64 bit executable (32 bit mode is forced only when using the GUI).

# **C Programming Libraries**

During the installation wizard on the CD-ROM the library files, user documentation and examples to the acting control PC in your test application are installed. You can also develop your test program on a different PC (in the "Demo/Offline Mode" of the software) and later upload your application to the control PC.

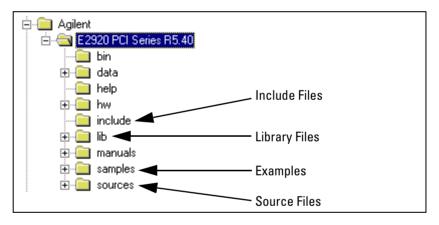

**Directory Structure**

All required files are automatically installed with the control software and can be found in the subdirectories of the Agilent PCI Series home directory. The following figure shows the directory structure on a Windows NT system.

The home directory is C:\Program Files\Agilent\E2920 PCI Series <Revision>.

When developing C programs for the testcard, you need to:

- Include the referring header files into your program.

- Enter the paths to include files, library files, and/or source files into the directory settings of your developing environment.

**Examples**

Many ready-to-use example programs can be found in the "**samples**" directory. The **user documentation** for hardware, software, and options uses many of these examples to explain the functions.

**Platform-Dependence**

All sample programs can be compiled with Microsoft ® VC++ 5.0.

Communication with E2920 series PCI testcards uses the E2920 series C-API. The C-API contains the necessary drivers for testcard communication. PCI C-API is available in binary form for a number of operating systems (including Windows NT), and as compilable source code for other systems. The platform and operating system determine which drivers are necessary for internal communication with the testcard and for the memory.

# **Generic C-API Functionality**

The C-API is used to program all analyzer, exerciser and performance optimizer functionalities.

For all features of the testcard, refer to:

- Agilent E2925B Opt. 300 PCI Exerciser User's Guide

- Agilent E2925B PCI Analyzer User's Guide

- Agilent E2925B Opt. 200 PCI Performance Optimizer User's Guide

# Protocol Permutation and Randomizer Functionality

The PCI Permutator and Randomizer software adds functions to the C-API for preparing and performing systematic functional tests at the protocol level, especially tests for exposing PCI devices of a computer system to variable stressful PCI traffic.

Developing computer systems requires a lot of different tasks and therefore involves a lot of people. This section outlines the process of computer system development and some roles of those who are involved in it. It shows the benefits of PCI Permutator and Randomizer software for each of them.

Computer system development requires the following steps:

#### • Device bring-up and debug

The development process starts with the bring-up and debug phase. In this phase the devices (add-in testcards, motherboard, and so forth) of a computer system are developed independently by testcard or chipset manufacturers. This phase includes electrical and PCI signal integrity tests and finishes with a **functional test phase** at the PCI protocol level.

**NOTE** Corner cases are exhaustive, complicated, and/or uncommon usage of PCI protocol elements, thereby indicating system limitations.

This test phase requires a well controllable (but artificial) testing environment. The devices are examined to see whether their protocol level behavior is as expected. The devices are tested on corner cases, whereby coverage of the test cases is well known. The tests are mainly performed by developers of research and development (R&D) departments.

#### System integration

After passing these tests, system integrators assemble systems from those testcards. The functionality of the testcards is tested in a **functional test phase**.

The PCI bus is the focus of these examinations, because it connects the motherboard to the peripheral devices within a computer system. Functional tests expose the PCI interfaces of devices and motherboard to PCI traffic.

The test checks whether the PCI devices of the computer system work as expected. One device after the other is examined, until each of them is exposed to certain functional tests. The tests consider their PCI compatibility and again the PCI behavior in corner cases at the protocol level.

#### • System quality assurance

In the last phase, the system is exposed to a **system assurance test**. In this phase, it is tested whether all parts of the system cooperate. Unlike a functional test, a system assurance test requires a realistic testing scenario. All components must transfer traffic simultaneously. The test result shows, whether the system crashes under this stress. For system assurance tests, stress tests and performance analysis are performed to find system bottlenecks.

NOTE Testing peripheral devices (such as graphic testcards, SCSI testcards, and LAN testcards) may cause some additional effort (for adapting device drivers or developing test software).

The PCI Permutator and Randomizer software provides functional tests for systems and devices at the PCI protocol level and system assurance tests.

When testing devices, mainly memory controlling mechanisms can be tested by focusing on host bridges and PCI-to-PCI-bridges.

### **Contributions of the PCI PPR Software**

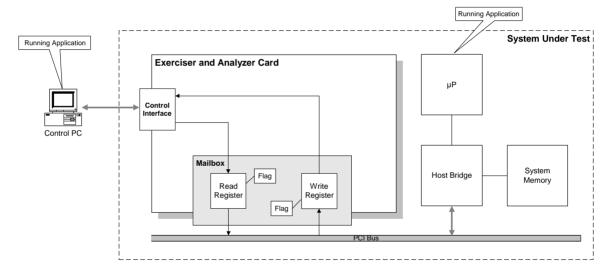

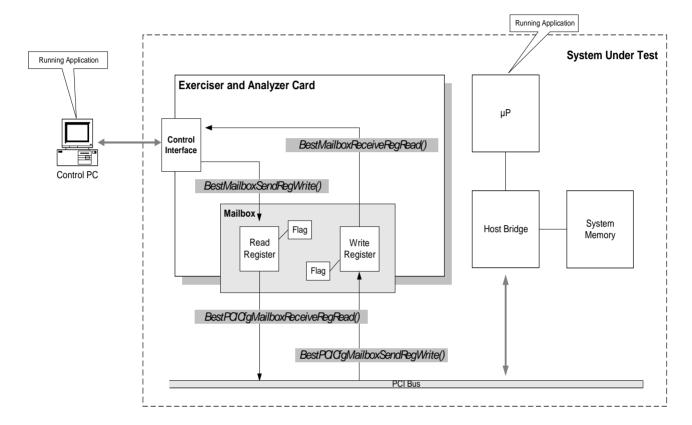

In this section, the particular role of the PCI Permutator and Randomizer software is explained. Therefore, it is shown how data transfer is controlled by the Exerciser and Analyzer.

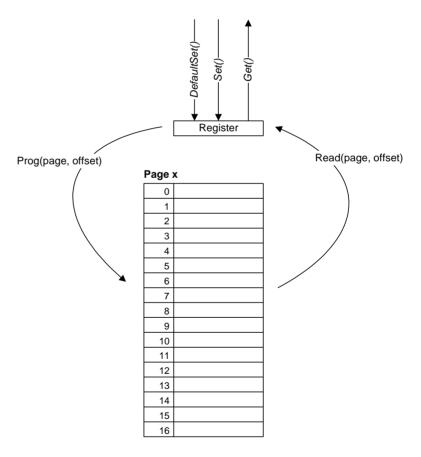

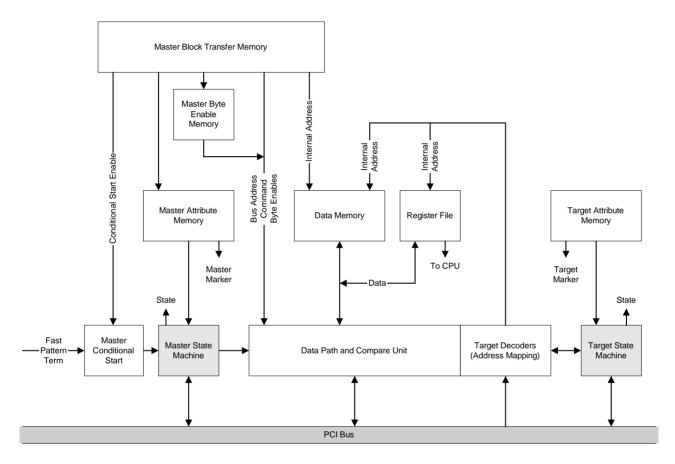

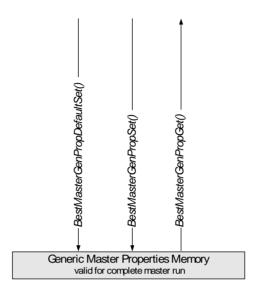

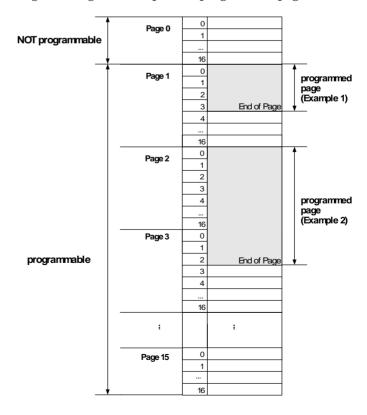

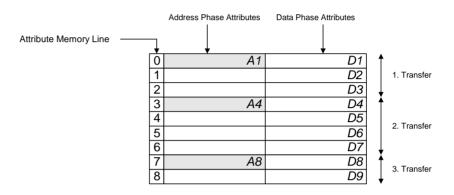

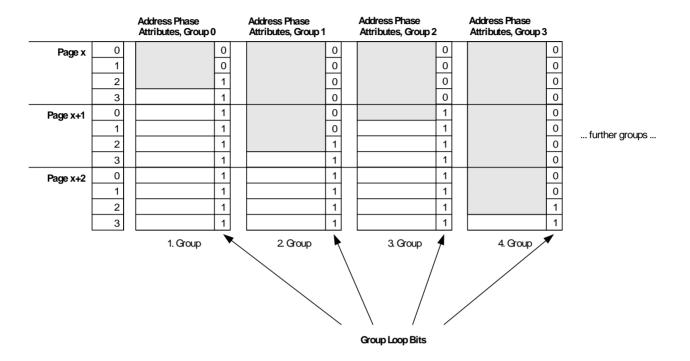

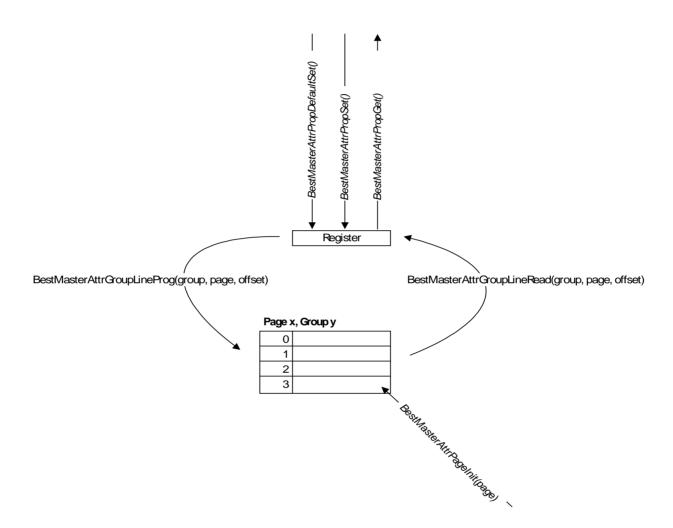

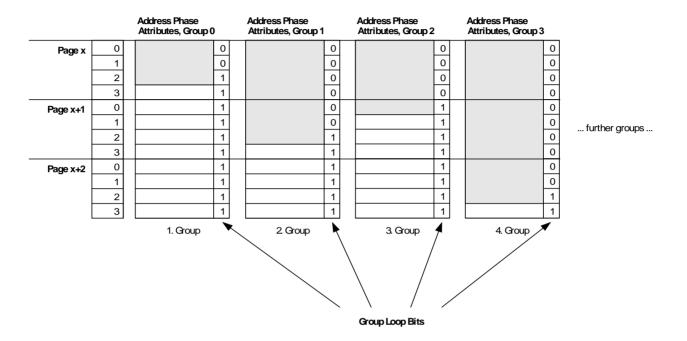

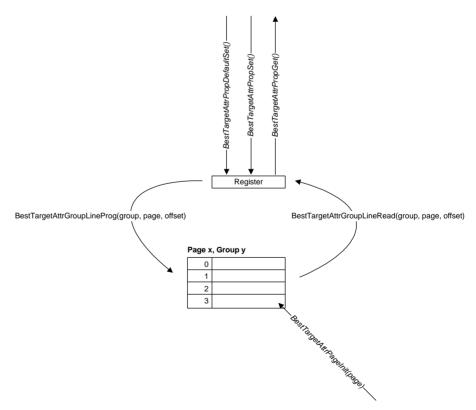

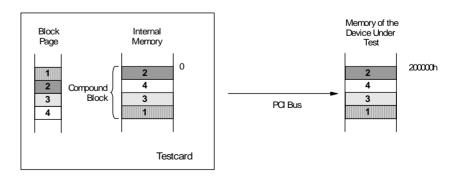

The test cases require systematically varying transfer parameters (commands, waits, burstlengths, byte enables, alignments). These parameters are controlled by the Exerciser and Analyzer. The information on how to control the parameters is held in programmable memories on the testcard:

- The master block transfer memory holds control information on how blocks are to be transferred when the Exerciser and Analyzer is used as master device (start address alignment, block size, byte enables, bus command). It also holds an entry pointing to a page in the master attribute memory, which is worked through during block transfer.

- The **master attribute memory** holds control information on master attributes on each phase of block transfer (burstlength, stepmode, wait inserting, parity/system error).

- The target attribute memory is used when the testcard is used as target device and holds control information on target attributes on each phase of a block transfer (parity/system error and terminations).

The PCI Permutator and Randomizer software programs these memories.

**NOTE** For more information on the memories, refer to "Programming the Exerciser" on page 75.

#### **Operation Principles**

Only the permutation constraints of attributes and block page parameters need to be set, then the permutation and randomizing algorithm first **calculates** whether all possible parameter combinations can be covered and estimates the testing time. The results of the calculation can be written into a textual **report**. If the algorithm calculated that not all necessary combinations can be covered, it can still be determined which combinations can be performed and which cannot.

The PCI Permutator and Randomizer software ensures that the device under test is exposed to all defined protocol variations, thus, PCI Permutator and Randomizer software determines the course of the test. The calculation can be repeated with varying parameters, until the results of the calculation of the PCI Permutator and Randomizer software meet your testing requirements. Then the PCI Permutator and Randomizer software can **build** and **download the pages** to the Exerciser and Analyzer.

To run the test, the PCI Permutator and Randomizer software is not required. This is done by the Exerciser and Analyzer's **exerciser run functions.** Errors that occur during the test (protocol errors, bus or device hang) can later be analyzed using Exerciser and Analyzer's **analyzer functions**.

### **Benefits**

When setting up tests, you can take advantage of the following features of the Exerciser and Analyzer and the PCI Permutator and Randomizer software:

#### • Creating controlled protocol corner cases

The software makes it possible to expose device or system under test to corner case traffic, to add system and parity errors, to assert and deassert signal lines and other.

Tests can be set up that add as many Exerciser and Analyzers as required and letting them transfer data blocks repeatedly to generate enough traffic to stress the PCI system.

#### • Data-integrity testing

The software makes it possible to use the Exerciser and Analyzer memory functions to comfortably write, read and compare data blocks.

#### • Emulating typical peripheral traffic

The software makes it possible to substitute test devices with Exerciser and Analyzers. Testcards can be set up to behave like any device. The memory is programmable with any content. There is no need to exchange devices in the system for testing reasons to get "realistic" traffic.

The PCI Permutator and Randomizer software intensifies the possibilities by systematically varying transfer parameters to examine protocol corner cases.

#### • Storing and analyzing bus traffic

The software makes it possible to find misbehavior on protocol and signal level using advanced listers (waveform lister, bus activity lister, transaction lister) of the (optional) graphical user interface of Exerciser and Analyzer. These listers allow a detailed analysis of all events that have occurred on the considered bus.

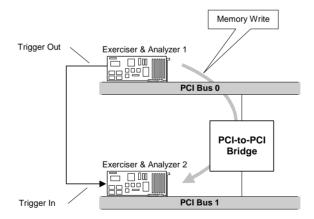

#### • Stressing from multiple PCI slots on multiple buses

The software makes it possible to use multiple testcards to generate stress traffic from one bus system to another over PCI-to-PCI-bridges.

#### • Deterministic and reproducible tests

In contrast to PCI traffic generated by other test devices, the generated variations are deterministic and reproducible. This guarantees coverage and reproducible tests. The permutation progress can be read out on block level or block page level. In the case of an error or a bus hang, exactly the same behavior can be repeated for reproduction of an error. Alternatively, the test can be continued after that error.

### PCI protocol attribute permutations within programmable constraints

The software makes it possible to specify the values to be varied for each master and target attribute separately. Thus, testing time can be reduced by focusing on cases of interest. Simple problems can soon be found.

#### • Detailed report

The software provides a printable report, which shows which protocol attributes are completely permutated against which other protocol attributes after how many of data transfers.

#### • Predictable testing time

The test's run time estimated by the PCI Protocol Permutation and Randomizer can also be written to the report.

# **Error Checking**

Each C-API function returns an error code. The error code is 0 (B\_E\_OK) if no error has occurred, otherwise it should be evaluated for error handling. Errors can be handled either by handle-based or non-handle-based error checking.

### **Handle-Based Error Checking**

Handle-based error checking provides better error messages than non-handle-based error reporting, so it should be used whenever possible. The following macro can be simplified if your program only uses a single handle.

Note that these macro definitions rely on the use of a global variable definition b\_errtype err.

**Used Macro**

Use a macro similar to this for handle-based error checking:

```

#define C1(handle, x) if ((err = x) != B_E_OK)\

{

printf ("%s (line %d)\n", \

BestLastErrorStringGet(handle), __LINE__);\

return -1;

}

```

This macro can be called in either one of the following ways:

- C1(handle 1,BestMasterGenPropDefaultSet(handle));

- err=BestMasterGenPropDefaultSet( handle ); C1(handle\_1, err);

Simplified Version of Handle-Based Error Checking In case you are using a single handle identified by the name *handle*, use the following macro:

```

#define C1(x) if ((err = x) != B_E_OK) \

{

printf ("%s (line %d)\n", \^

BestLastErrorStringGet(handle), __LINE__);\

return -1;

}

```

This macro can be called in either one of the following ways:

- C1(BestMasterGenPropDefaultSet( handle ));

- err=BestMasterGenPropDefaultSet( handle ); C1(err);

Error Checking Programming Overview

### **Non-Handle-Based Error Checking**

The following functions do not provide handles, therefore they cannot be used with handle-based error checking methods:

- BestDevIdentifierGet()

- BestPCICfgMailboxReceiveRegRead()

- BestPCICfgMailboxSendRegWrite()

Handle Initialization

The following function initializes the handle. The handle is valid only if this function returns the handle successfully:

• BestOpen()

Ilsed Macro

Use all the functions with a macro similar to this:

```

#define C(x) if ((err = x) != B_E_OK) \

{

printf ("%s (line %d)\n", \

BestErrorStringGet(handle), __LINE__);\

return -1;

}

```

This macro can be called in either one of the following ways:

- C(BestDevIdentifierGet(ven, dev, no, &devid));

- err=BestDevIdentifierGet(ven, dev, no, &devid); C(err);

For error codes, refer to "b\_errtype" in the C-API/PPR Programming Reference.

### **Example: Using the C-API**

**NOTE** The following example can be used as framework for all further code fragments using the C-API in this document.

```

#include <stdio.h>

#include <mini api.h>

define CH(x) if ((err = x)) != B E OK \setminus

{printf ("%s (line %d)\n", \

BestLastErrorStringGet(handle), LINE );\

return -1; }

\#define C(x) if ((err = x)) != B E OK \

{printf ("%s (line %d)\n", \

BestErrorStringGet(handle), LINE );\

return -1;

int main ()

b errtype err;

b charptrtype version string;

b handletype handle;

/* Open the communication session to testcard, initialize */

/* internal structures. */

err = BestOpen(&handle,B PORT RS232,B PORT COM1); C(err);

/* If using RS232, set baud rate: */

err = BestRS232BaudRateSet(handle,B BD 57600); CH(err);

/* For example:*/

/* Read product & serial number from testcard. */

err = BestVersionGet (handle, B VER PRODUCT, &version string);

CH(err);

printf("Product: %s\n", version string); err = BestVersionGet

(handle, B VER SERIAL, &version string); CH(err);

printf("Serial#: %s\n", version string);

/* Close the session to deallocate memory. */

err = BestClose(handle); CH(err);

```

# **Example: Using the PPR**

**NOTE** The following example can be used as framework for all further code fragments using the PPR in this document.

#### WARNING

This program fragment writes data to system memory. To run this program in a real environment, a line that allocates the required memory must be added.

```

#include <stdio.h>

#include <mini api.h>

#include <ppr.h>

#define CHECK { if (status != B E OK)

{printf ("ERROR line %d, %s\n", LINE ,

BestErrorStringGet(status) ); return -1;}\

#define WARN { if (status != B E OK)

{printf ("WARNING

line %d, %s\n", LINE , BestErrorStringGet(err) );} \

int main ( void )

b errtype status;

b handletype handle;

b int32

status reg;

b int32

errbit;

b int32

count;

b_charptrtype errtext;

b int32

blockruns:

/* Open the communication session to testcard on Fasthost

interface.*/

status = BestOpen( &handle, B PORT PARALLEL,

B PORT LPT1); CHECK;

/* Set attribute mode to sequential. */

status=BestMasterGenPropSet( handle,

B MGEN ATTRMODE,

B ATTRMODE SEQUENTIAL); CHECK;

/* Initialize PPR. */

status=BestPprInit (handle); CHECK;

```

```

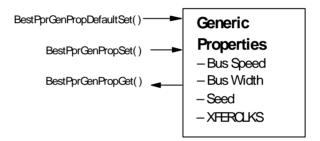

/* Set up generic PPR properties. */

status=BestPprGenPropSet( handle, BPPR GEN BUSWIDTH, 32 );

CHECK;

/* Block permutation.

* Data is transfered from testcard internal address 0

* to busaddress 0xb8000 (video memory). */

printf ("programming Block permutation\n");

status=BestPprBlockPermPropSet(handle,

BPPR BLK DIR,

BPPR DIR WRITE ); CHECK;

status=BestPprBlockPermPropSet( handle,

BPPR BLK BUSADDR,

0x0b8000 ); CHECK;

status=BestPprBlockPermPropSet( handle, BPPR BLK INTADDR, 0 );

status=BestPprBlockPermPropSet( handle, BPPR BLK NOFDWORDS, 64 );

CHECK;

status=BestPprBlockPermPropSet( handle, BPPR BLK ATTRPAGE, 2 );

CHECK;

status=BestPprBlockPermPropSet( handle, BPPR BLK PAGENUM, 1 );

CHECK:

status=BestPprBlockPermPropSet(handle, BPPR BLK PAGESIZEMAX, 60);

CHECK;

status=BestPprBlockPermPropSet( handle, BPPR BLK CACHELINE, 4);

CHECK;

/* Block variation properties. */

status=BestPprBlockVariationSet( handle,

BPPR BLK ALIGN,

"(%16=0), (%16=4), (%16=8), (%16=12), (%32=0)",

BPPR ALG PERM); CHECK;

status=BestPprBlockVariationSet( handle,

BPPR BLK SIZE,

"4,8,16",

BPPR ALG PERM ); CHECK;

status=BestPprBlockVariationSet( handle,

BPPR BLK CMDS,

"mem write, mem writeinvalidate",

BPPR ALG PERM ); CHECK;

status=BestPprBlockGenerate( handle ); CHECK;

```

```

/* Master attribute permutations. */

printf ("Programming master attr. permutation\n");

status=BestPprMAttrPermPropSet( handle,

BPPR MA PAGENUM, 2 ); CHECK;

status=BestPprMAttrPermPropSet( handle,

BPPR MA PAGESIZEMAX, 49 ); CHECK;

status=BestPprMAttrVariationSet( handle,

B M LAST,

"4, 8, 32",

BPPR ALG PERM ); CHECK;

status=BestPprMAttrVariationSet( handle,

B M WAITS,

"0, 1, 3, 8",

BPPR ALG PERM ); CHECK;

status=BestPprMAttrVariationSet(handle,

B M STEPS,

"0, 7",

BPPR ALG PERM ); CHECK;

status=BestPprMAttrVariationSet( handle,

B M TRYBACK,

"true, false",

BPPR ALG PERM ); CHECK;

/* Generate master attributes page. */

status=BestPprMAttrGenerate( handle ); CHECK;

/* Print a report w/o target attributes. */

status=BestPprReportPropSet (handle, BPPR REP TA, 0); CHECK;

status=BestPprReportPropSet (handle, BPPR REP TACONTENT, 0);

CHECK;

status=BestPprReportFile(handle, "report.txt"); CHECK;

```

```

/* Obtain number of blockruns necessary for complete coverage. */

status=BestPprMAttrResultGet( handle,

BPPR MA RUNS,

&blockruns );

printf ("Running master %u times\n", blockruns);

for (count=0; count<blockruns; count++)</pre>

status=BestMasterBlockPageRun(handle, 1); CHECK;

do

status=BestStatusRegGet(handle, &status reg); CHECK;

while ( (status reg & 0x01) );

if (status reg & 0x80)

printf ("Test failed, master abort has occured!\n");

break;

/* Get protocol errors. */

if (status reg & 0x10)

/* protocol error occured */

status=BestObsStatusGet (handle, B OBS ACCUERR, &status reg);

CHECK;

printf("The following protocol errors habe been detected:\n");

for (errbit=1;

errbit<=0x010000000; errbit >>=1)

if (status reg & errbit)

status=BestObsErrStringGet (handle, errbit, &errtext); CHECK;

printf ("%s\n", errtext);

/* Close the session, deallocate memory. */

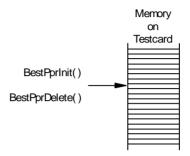

status=BestPprDelete( handle ); CHECK;

status=BestClose( handle ); CHECK;

```

# Programming the Framework

The following sections provide information about the testcard's connection to a control PC and its initialization. These are the first steps to be performed in any C program for the testcard.

- "Connection and Initialization" on page 28 shows you to set up and specify the control interface(s) and how to establish the connection.

- "Administration" on page 33 gives information about performing several checks, such as checks for enabled capabilities of the testcard, for current versions of testcard's components or for system information.

Here you get also information about resource locking.

- "Power-Up and Reset Control" on page 37 shows how to control the testcard's power-up and reset behavior.

- This information is useful for tests focusing on the power-up behavior of your system under test. It can also help when the testcard hangs and you need to unlock it.

- "Card Status Register Access" on page 42 gives information about using the testcard's status register.

- This information is useful for evaluating test results or for debugging and evaluating errors.

### **Connection and Initialization**

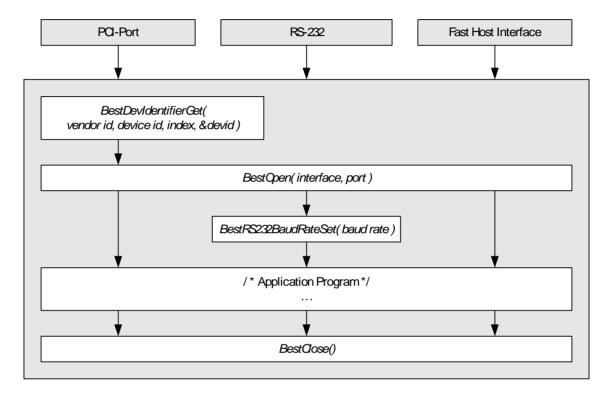

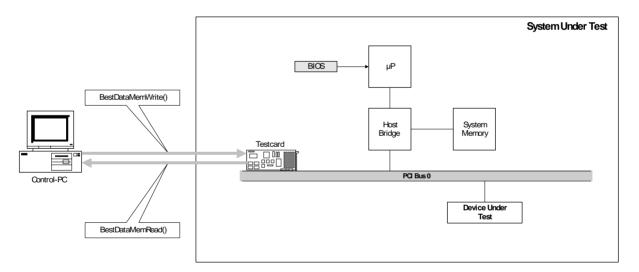

When executing a C program for the testcard, the testcard and the connections must be initialized. The testcard can be controlled via PCI port, RS-232 serial interface or Fast Host Interface. Some typical initialization routines for each type of control connection are shown in "Examples" on page 30.

**PCI Port** The testcard communicates via the PCI bus through its configuration space.

No system resources are required to program the testcard. This is especially useful when the testcard is used as a passive observer (protocol checker or performance monitor) and is not authorized to change the system configuration of the system under test (for example, memory mapping).

RS-232 Serial Interface The RS-232 serial interface provides an easy-to-use control interface, which is available on all PCs and notebook computers. It can be run at 2400, 4800, 9600, 19200, 38400, and 57600 baud (8 bit data, 1 stop bit, no parity).

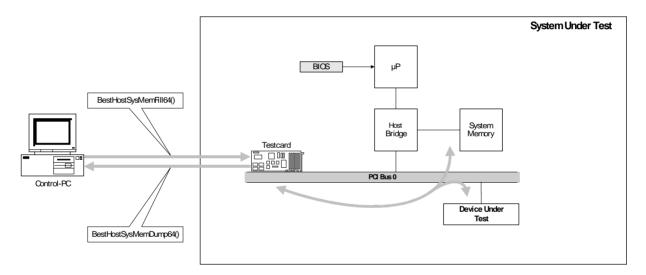

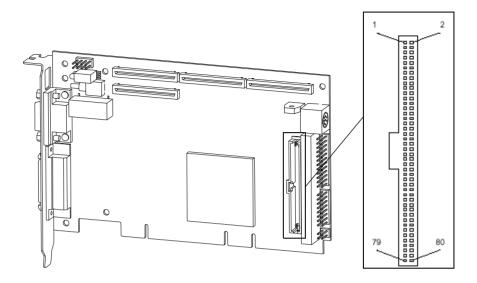

The Fast Host Interface port provides an easy-to-install connection to a standard PC with higher throughput than an RS-232 interface in both read and write directions.

The control PC must be equipped with the Fast Host Interface card coming with the PCI Analyzer and connected to the parallel port on the testcard.

**Specification** Maximum transfer rate: 4 MB/s (using the Fast Host Interface).

\_\_\_\_\_

Fast Host Interface Port

### **Functions Overview**

The following figure shows the available functions used for connecting and initializing the testcard. This figure also shows the integration of these functions into the test program.

**Programming Steps**

Initializing the Exerciser and Analyzer testcard requires the following steps:

- 1 If the PCI Bus is used as the controlling interface port, use BestDevIdentifierGet to get the device number of the testcard. This device number is used in BestOpen for device identification.

- **2** Initialize internal structures and variables for the control port and establish the connection. Use *BestOpen*.

- **3** If the **RS-232** serial interface is used, set the baud rate with *BestRS232BaudRateSet*.

- 4 Insert your application code.

- Parts of your program may communicate with different resources via different ports on the testcard. Therefore, resources must be locked while they are used and unlocked after they have been used. Use <code>BestResourceLock</code> and <code>BestResourceUnlock</code>.

- **5** Close the connection and deallocate the session memory with *BestClose*.

### **Examples**

The following examples show the programming steps required to initialize the testcard, and to set up a control connection to it. An example is given for each type of control connection:

- serial

- parallel

- PCI port

Note that for clearness and convenience the errors are handled assuming that only one connection has been opened and the session handle is named "handle". This also enables compatibility with previous program versions.

### **Serial Port Example**

In this example, a connection to the testcard is opened using the serial port and the baud rate is set to 57600 bps.

**Implementation**

```

#include <stdio.h>

#include <mini api.h>

int main ()

b errtype err;

b_handletype handle;

/*Initialize port internal structs and variables*/

err=BestOpen(&handle,B PORT RS232,B PORT COM1); C(err);

/*Set baud rate to 57600*/

err=BestRS232BaudRateSet(handle,B BD 57600); C(err);

/* Start of application program code, for example, locking the

exerciser */

err=BestResourceLock (handle, B RESLOCK EXERCISER); C(err);

/* This line represents the application program for the exerciser

/\star After exerciser application program's end, unlock the exerciser

err=BestResourceUnlock(handle, B RESLOCK EXERCISER); C(err);

/* close the session and deallocate memory*/

err=BestClose(handle); C(err);

```

### **Fast Host Interface Example**

**Task** The following example shows how to open a connection to the testcard using the Fast Host Interface.

**Implementation** #include <stdio.h> #include <mini api.h> int main ( ) b errtype err; b handletype handle; /\*Initialize port internal structs and variables\*/ err=BestOpen(&handle,B PORT FASTHIF,0); C(err); /\* Start of application program code, for example, locking the exerciser \*/ err=BestResourceLock (handle,B\_RESLOCK\_EXERCISER); C(err); /\* This line represents the application program for the exerciser \*/ /\* After exerciser application program's end, unlock the exerciser err=BestResourceUnlock(handle, B\_RESLOCK\_EXERCISER); C(err); /\* close the session and deallocate memory\*/ err=BestClose(handle); C(err);

# PCI Bus Example With Two Testcards and Reading Out Capabilities

**Task** The following example opens a connection to two testcards using the PCI interface. *BestDevIdentifierGet* is used to request the **device identifier** of each testcard. This device identifier is then used to open the connection to the respective testcard.

The third parameter of *BestDevIdentifierGet* is an **index** used for testcard identification when multiple testcards are used.

The example also shows how to read out the testcard's capabilities.

**Implementation**

```

#include <stdio.h>

#include <mini api.h>

int main ()

b errtype err;

b handletype handle1, handle2;

b int32 devid;

b int32 capability code;

/*Get device number devid of first testcard

The index (number=0) can be used to distinguish between

multiple testcards*/

err=BestDevIdentifierGet(0x103C, 0x2926, 0, &devid); C(err);

/*Initialize port internal structs and variables*/

err=BestOpen(&handle1, B PORT PCI CONF, devid); C(err);

/*Repeat for the second testcard (number=1)*/

err=BestDevIdentifierGet(0x103C, 0x2926, 1, &devid); C(err);

err=BestOpen(&handle2, B PORT PCI CONF, devid); C(err);

/* Application program code, check here for capabilities */

err=BestCapabilityRead(handle1, &capability_code); C(err);

(capability code & (B CAPABILITY EXERCISER | B CAPABILITY ANALYZER))

printf("testcard1:");

printf("exerciser capability enabled or ");

printf("analyzer capability enabled (or both) !\n");

else

printf("testcard1: Neither exerciser nor analyzer capability

enabled !\n");

```

### **Administration**

You can prepare the following during the initialization phase of your C program.

**Version Checking**

Before your program starts actions on the testcard, you can let it check for versions of the testcard's components.

To ensure compatibility of hardware, firmware and C-API software, you can check for the versions of the following components of the testcard.

- Card's product number

- Hardware serial number

- Card version

- Core BIOS

- Firmware version and date

- XILINX FPGA (Field Programmable Gate Array) chain architecture

- C-API version

#### **Resource Locking**

The C program can access different resources on the testcard via different interfaces. To guarantee proper operation, you can lock different resources to different interfaces. This prevents the resources from being simultaneously accessed via different ports.

#### **Capability Checking**

In offline mode, the C program can run without an testcard and/or without the required product capabilities. This may be useful, for example, for testing or demo purposes. You can check for available product capabilities in your program's initialization phase.

The C-API allows you to check whether or not the following capabilities are available:

- All capabilities

- · No capabilities

- Analyzer

- Exerciser

- Host interface (CPU port, static I/O, host access functions)

- 64-bit PCI

- 66-MHz PCI (for exerciser and analyzer)

- · Trace memory sizes

- Performance measures

It is a good idea to have this information available before you call support.

If your hardware does not have one or more of the above capabilities, you can still develop or test in offline mode, because this mode does not use a physical port and, therefore, does not require hardware.

#### **System Checking**

The C-API also enables you to request the buswidth (32 or 64 bits) and speed (33 or 66 MHz) of the PCI system under test.

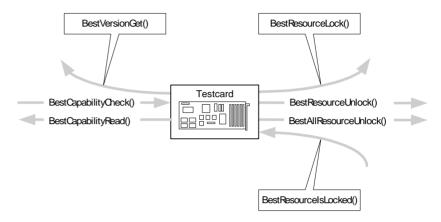

### **Functions Overview**

The following figure shows all functions available for administration purposes regarding to the testcard and the system under test.

**Programming Options**

The administration functions of the testcard allow the following options:

- To ensure compatibility of hardware, firmware and C-API software, or in case of support calling, check the version of testcard's components. Use *BestVersionGet*.

- To lock different resources to different interfaces, use BestResourceLock.

- To unlock resources or to check whether resources are locked, use BestResourceUnlock, BestAllResourceUnlock and BestResourceIsLocked.

- To check for a special available capability such as Analyzer or Exerciser, use *BestCapabilityCheck*.

- To get information about all available capabilities, use BestCapabilityRead.

- To get system information, such as buswidth and busspeed, use BestSystemInfoGet.

### **Examples**

Task The following code fragments give examples for administration purposes.

Version Checking /\* Read product & serial number from testcard \*/

err=BestVersionGet (handle, B\_VER\_PRODUCT, &version\_string); C(err);

printf("Product: %s\n", version\_string);

```

err=BestVersionGet (handle, B_VER_SERIAL, &version_string); C(err);

printf("Product: %s\n", version_string);

err=BestVersionGet (handle, B_VER_SERIAL, &version_string); C(err);

printf("Serial#: %s\n", version_string);

/* Locking the exerciser */

err=BestResourceLock (handle, B_RESLOCK_EXERCISER); C(err);

/* This line represents the application program for the exerciser */

err=BestResourceUnlock(handle, B_RESLOCK_EXERCISER); C(err);

Capability Checking /* Application program code, check here for capabilities*/

err=BestCapabilityRead(handle1, &capability_code); C(err);

if

(capability_code & (B_CAPABILITY_EXERCISER | B_CAPABILITY_ANALYZER))

{

```

if

(capability\_code & (B\_CAPABILITY\_EXERCISER | B\_CAPABILITY\_ANALYZER))

{

printf("testcard1:");

printf("exerciser capability enabled or ");

printf("analyzer capability enabled (or both) !\n");

}

else

{

printf("testcard1: Neither exerciser nor analyzer capability enabled !\n");

}

}

System Checking

/\* Checking for the bus speed \*/

berr=BestSystemInfoGet(handle,B SINFO BUSSPEED,&BusSpeed); C(err);

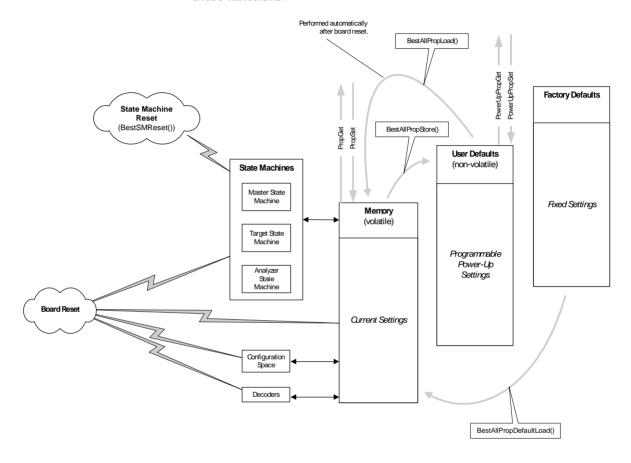

# **Power-Up and Reset Control**

The behavior of the testcard during power-up or reset can be controlled by programming power-up properties. Controlling this behavior is then needed when writing C programs that focus on the power-up behavior of the system under test, or when the PCI bus hangs making a reset necessary.

The following properties are available to control power-up and reset:

#### • Power-Up

After power-up, the testcard is completely reset. The testcard's configuration space header settings control the behavior of the testcard after power-up with property B\_PU\_CONFRESTORE. Set this property according to your test environment before you power down the testcard:

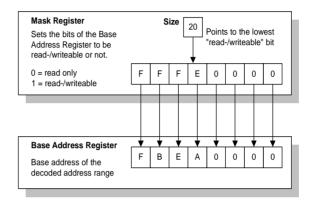

- If the testcard is used in a PCI system with BIOS, then the BIOS-programmable bits in the base address registers of the testcard should be set to 0 for power-up—that is: these bits should not be restored from the settings before power-up. The BIOS can reprogram them when allocating memory resources during system configuration.

- In a system without BIOS, you must set these bits to allocate memory resources. They should be programmed in such a way (using the power-up properties) that they do not need to be reprogrammed after each power-up.

For information on the configuration space header, refer to "Configuration Space Header" in the *PCI Exerciser User's Guide*.

#### • PCI Reset

Normally, a PCI reset is issued by the system controller of the system under test and has the same effect as power-up.

However, property B\_BOARD\_RSTMODE can be used to prevent the testcard from being completely reset, for example, to avoid loss of data or change of states. That means that only the internal state machines and the target are reset and initialized; the master and trace memory are not automatically reset because they are controlled by their own power-up properties.

• Board Reset and Statemachine Reset commands

These commands issue an testcard reset from the C program:

The *Board Reset* command is used to establish a defined state of the testcard before the C program actually begins. The command has the same effect as power-up, however, it does not affect the configuration space settings or internal state machines.

The *Statemachine Reset* command can be used before recovering data from the testcard if the testcard does not react anymore because of a hanging PCI bus.

**Restoring Settings after Resets**

The testcard's behavior is determined by property settings in its **memory**. These settings are currently influenced internally by programming, or externally by the test flow.

Because the testcard's memory is volatile, the current property settings are lost after the testcard is reset. To ensure a deterministic behavior during power-up, power-up settings are automatically loaded from a non-volatile, programmable memory. These settings are referred to as **user defaults** and allow a programmable power-up behavior of the testcard.

However, the user defaults could also be set in a way that causes start-up problems with the system under test or the testcard. In this case, **factory defaults** can be used instead.

## **Functions Overview**

The following figure shows all functions used to program power-up and reset behavior of the testcard and displays all memories controlled by these functions.

**Programming Options**

The power-up control of the Exerciser and Analyzer testcard allows the following options:

- To program the user defaults, store the current settings as power-up defaults with *BestAllPropStore*.

- To use the user defaults as current settings, load them to the memory with *BestAllPropLoad*.

- To use the factory defaults as current settings, load them to the memory with *BestAllPropDefaultLoad*.

- To issue a board reset and a state machine reset, use *BestBoardReset* and *BestSMReset*.

- To determine whether a PCI reset causes a board reset or a state machine reset, set the "board mode" with *BestBoardPropSet*.

## **Examples**

The testcard's behavior is determined by property settings in its **memory**. These settings are currently influenced internally by programming, or externally by the test flow.

The following examples shows how to define the power-up behavior of the testcard:

- "Factory Defaults for Power-Up" on page 40

The user defaults can be set in a way that causes start-up problems with the system under test or the testcard. In this case, factory defaults can be used instead.

- "User Defaults for Power-Up" on page 41

Because the testcard's memory is volatile, the current property settings are lost after the testcard is reset. To ensure a deterministic behavior during power-up, power-up settings are automatically loaded from a non-volatile, programmable memory. These settings are referred to as **user defaults** and allow a programmable power-up behavior of the testcard.

## **Factory Defaults for Power-Up**

The following example shows how to program the testcard to use the factory defaults for power-up.

```

Implementation  /* Load the factory defaults as current settings. */

err=BestAllPropDefaultLoad( handle ); C(err);

/* Load the current settings (now acting as the factory defaults)

as user defaults. */

err=BestAllPropStore( handle );C(err);

/* Reset the board and uses the factory defaults as power-up

settings. */

err=BestBoardReset( handle );C(err);

```

#### **User Defaults for Power-Up**

Instead of using the factory defaults, you can program *any* user defaults according to your specific test requirements. All functions described in the C-API reference the names of which end with ...PropSet() write current settings to the memory. This is shown in the following example.

```

Implementation

int main (int argc, char *argv[])

b errtype err;

b handletype handle;

err=BestOpen(&handle,B PORT PARALLEL,B PORT LPT2); C(err);

err=BestConnect ( handle ); C(err);

/* Set vendor and device id:*/

err=BestConfReqSet(handle, 0x00, 0x2925103c); C(err);

/* Make Device and Vendor ID read-only.*/

err=BestConfRegMaskSet(handle, 0x00, 0x00000000); C(err);

/* Read/write bits will have their factory default values at

powerup. */

err=BestPowerUpPropSet(handle, B PU CONFRESTORE, 0); C(err);

err=BestAllPropStore(handle); C(err);

/* Disconnect from the current port.*/

err=BestDisconnect (handle); C(err);

/* Close the session and deallocate memory.*/

err=BestClose(handle); C(err);

return 0;

```

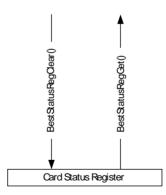

# **Card Status Register Access**

The testcard status register can be used, for example, to evaluate the test result after the test run, and to debug and evaluate errors. The bits show:

- the exerciser status: master run, active target, data compare error, or master block abort.

- the analyzer status: protocol error, trace memory is running (recording), asserted interrupts.

- whether a C function returned an error (error code not equal to zero).

- whether a high level test function (see Built-In Test Functions) has failed.

- whether another on-board application has failed.

- whether a PCI interrupt has occurred.

For the content of the status register, refer to "Testcard Status Register" in the Agilent E2925B Opt.320 C-API/PPR Reference.

## **Functions Overview**

The following figure shows the functions available to access the status register of the testcard.

**Programming Steps**

Executing a test program requires access to the testcard status register as follows:

- 1 Before executing the test program, clear all bits of the testcard status register with *BestStatusRegClear* to ensure a definite register condition. All bits are set to 1.

- **2** After executing the test program, read the whole content of the testcard status register with *BestStatusRegGet*.

## **Example**

The following lines show how to poll the status register to detect the end of a master run.

```

do

{

err=BestStatusRegGet(handle, &statusreg); C(err);

}

while(statusreg & 0x01);

```

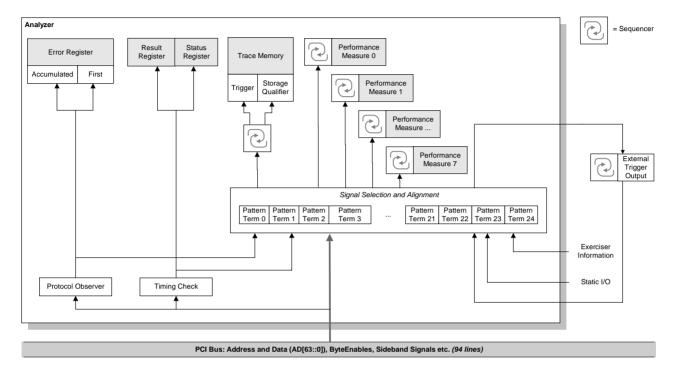

# Programming the Analyzer

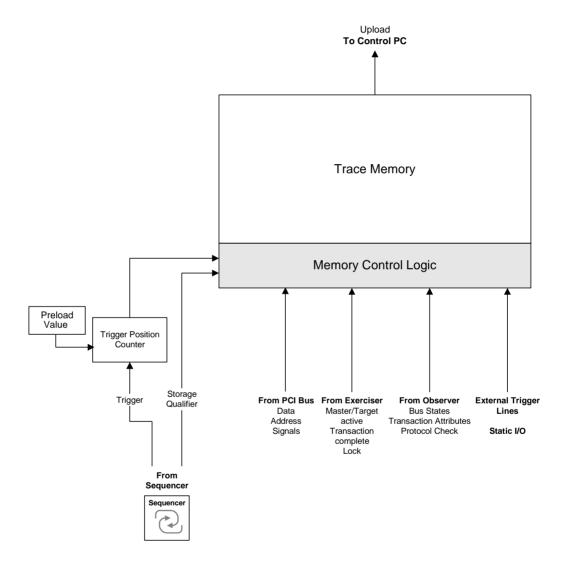

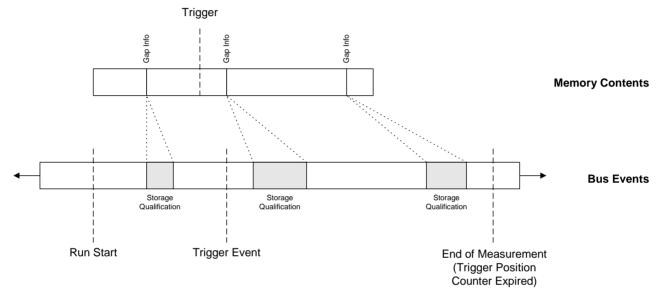

The task of the PCI analysis is to monitor the PCI bus, to detect specific events, to measure and evaluate the occurrences of signals on the bus. The following sections explain how to program the components of the testcard's analyzer fulfilling the different tasks:

- "Protocol Observer Programming" on page 47 explains how to mask rules to be observed and how to read the observer result registers.

- "Timing Check Programming" on page 49 explains how to set up the timing check, and how to get the results.

- "Programming the Pattern Terms" on page 52 explains all types of pattern terms, and how to use and program them.

- "Sequencer Programming" on page 55 explains how to program the sequencers.

- Basically, all sequencers on the testcard work in the same manner. There are many parameters controlling the sequencers. The principles of the sequencers are explained, and an example of using the trace memory trigger sequence is provided to show how to program the sequencers.

- "Performance Measurement Programming" on page 64 explains how to program the performance measures.

- "Trace Memory Programming" on page 70 explains how to use the trace memory and how to program its sequencer and the storage qualifier. How to upload and evaluate the contents of the trace memory is also shown.

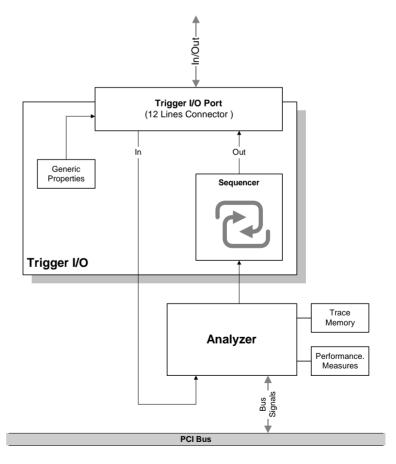

**Analyzer Components**

The following figure shows the components of the Analyzer with its inputs and outputs and from where the results of the analysis can be taken.

#### Inputs are:

- 94 line PCI signals: address and data lines, byte enables, sideband signals and so forth

- additional information generated by the observer

- exerciser signals: master and target marker, different outputs from their statemachines, and so forth.

- 12 line external trigger input

- 8 line static I/O

#### **Results** can be taken from:

- Result and Error Registers

- Trace Memory

- Performance Measures

The **outputs** can be used to trigger external devices.

The analyzer and exerciser of one testcard can be used in parallel. This allows you to set up the analyzer to monitor **exerciser** transactions.

# **Protocol Observer Programming**

The protocol observer monitors 53 different protocol rules simultaneously. The protocol rules refer to PCI specification rules. An "any error" output for triggering purposes is provided, as well as registers to latch the first occurring errors and the accumulating subsequent errors.

#### **Error Register Contents**

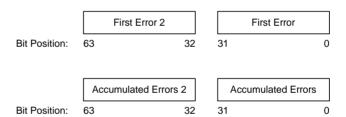

The protocol observer provides two error registers containing:

- Bits for the protocol rule violations that have occurred first. Often the

first rule violations are the reason for subsequent rule violations.

Each individual rule can be masked from being detected as "first rule

violation". This allows you to exclude rule violations prior to those of

your interest from triggering the analyzer.

- A flag bit for each rule violated during observation.

#### **Error Register Design**

Both of the following registers hold a flag bit for each rule and, therefore, consist of two registers each with a length of 32 bits.

The contents of the error registers can be read by means of the testcard C-API, which converts it into a text string describing the violated rule.

#### Further Use A detected p

A detected protocol violation can:

- be used as input for pattern terms (see "Programming the Pattern Terms" on page 52).

- trigger the trace memory (see "Trace Memory Programming" on page 70).

The rule violation(s) cause a "bus error", which can be used as a trigger signal. It is aligned to the first clock at which the error was detected.

This holds true except for parity errors: they are aligned to the transfer cycle where data does not match the PAR signal. Using a storage qualifier allows for storing only the incorrect data phases.

### **Functions Overview**

The Agilent E2925B testcard's programming interface provides functions for programming the protocol observer. The available functions and their usage is shown by describing the programming steps.

**Programming Steps**

Programming the protocol observer requires the following steps:

- **1** Set the observer properties.

- To ensure that all protocol rules will be observed, set all mask bits to 0. Use BestObsDefaultSet.

- 2 Specify a mask.

Set the protocol rules to be ignored in the "first error register". Use *BestObsMaskSet*.

**3** Request the protocol errors.

To determine whether rules have been violated, check whether the "first error" result registers in the observer status register hold a value. Use *BestObsStatusGet*.

**4** Request the error string.

To read the errors, convert the information read from the registers into a text string and send it, for example, to a file or to standard output.

${\bf Use} \ {\it BestObsErrResultGet}.$

## **Example**

**Task** Set up the protocol observer to mask the PARITY\_1 rule, read the detected protocol errors and print the error string.

```

Implementation

```

```

/* Set the observer properties to their default values. */

err=BestObsPropDefaultSet(handle); C(err);

/* Specify a Mask: Mask the rules PARITY_1 by setting their bits in

the mask register to 1 */

err=BestObsMaskSet(handle, B_R_PARITY_1, 1); C(err);

/* Check the value in the "first error" result registers in the

observer status register. */

err=BestObsStatusGet( handle, B_OBS_FIRSTERR, &firsterr1); C(err);

err=BestObsStatusGet( handle, B_OBS_FIRSTERR2, &firsterr2); C(err);

```

```

/* Read the lower bits of the accumulated error register. */

err=BestObsStatusGet(handle, B_OBS_ACCUERR, &accuerr1); C(err);

/* Read the upper bits of the accumulated error register. */

err=BestObsStatusGet(handle, B_OBS_ACCUERR2, &accuerr2); C(err);

/* Clear the observer status register. */

err=BestObsStatusClear(handle); C(err);

/* Print the error string using the error register values. */

err=BestObsErrResultGet( handle, accuerr1, accuerr2, &errtxt); C(err);

printf ("Protocol error: %s\n", errtxt);

```

# **Timing Check Programming**

The testcard checks the PCI bus for setup and hold timing violations in real-time. Checking is always performed while the testcard is powered. You can disable individual signals if their observation interferes with your test.

For a list of all available signals, refer to "b\_signaltype (for Timing Check)" in the Agilent E2925B Opt. 320 C-API/PPR Reference.

**NOTE** At present, the timing check is only available for 33 MHz PCI busses.

## **Functions Overview**

The Agilent E2925B testcard's programming interface provides functions for programming the timing checker. The available functions and their usage is shown by describing the programming steps.

#### **Programming Steps**

Programming the timing checker requires the following steps:

1 Enable all signals and preset the set-up and hold time to the values according to the PCI Specification.

Use BestTimCheckDefaultSet.

**2** To set-up and hold time to values other than the PCI Specification defaults, set the generic timing check properties to allow changes. Use *BestTimCheckGenPropSet*.

**3** To select the signals to be checked for your test, mask the signals that are not relevant.

Use BestTimCheckMaskSet.

**4** Set up the timing parameters in the preparation register. Use *BestTimCheckPropSet*.

**5** Write the settings to the testcard.

Use BestTimCheckProg.

**6** To determine whether the PCI frequency is stable enough for a proper timing check, read the timing check status .

Use BestTimCheckStatusGet.

**NOTE** The result registers of the timing check are cleared automatically and the check is continued with the new parameters.

**7** Determine whether a timing violation has occurred and print the textual report.

${\bf Use} \ {\it BestTimCheckResultGet}.$

## **Example**

**Task** Program a timing check against a set-up time of 6 ns and a hold time of -250 ps at a bus speed of 33 MHz.

```

Implementation

/* Set the timing check to default values. */

BestTimCheckDefaultSet(handle);

/* Set the generic timing check property. */

BestTimCheckGenPropSet(handle, B TCGEN SPEC, 0);

/* Set up the timing parameters in the preparation register and

write them to the card. */

BestTimCheckPropSet(handle,B TC SETUP TIME,6000);

BestTimCheckPropSet(handle,B TC HOLD TIME,250);

BestTimCheckPropSet(handle, B TC HSIGN, 1);

BestTimCheckProg(handle);

At this point of the program, it is expected that some traffic can be found

on the PCI bus to see whether signals are violated.

/* Read the timing check status to determine whether the PCI

frequency is stable enough for a proper timing check. */

BestTimCheckStatusGet(handle,B TC TCSTAT,&status);

if (status & B TC ERROR)

printf("Timing checker data incorrect because frequency has

changed !\n");

exit (1);

/* Determine whether a timing violation has occurred and print a

textual report. */

if (status & B TC VIOLATION)

printf("Timing violation occurred\n");

BestTimCheckResultGet(handle,&errorreport);

printf("%s\n",errorreport);

```

# **Programming the Pattern Terms**

The pattern terms are programmed using logical equations that define the pattern to be recognized. Each pattern term is identified by its pattern term identifier (pt0 ... pt23). For a list of valid pattern term identifiers, see "Pattern Term Identifiers" in the Agilent E2925B Opt. 320 C-API/PPR Reference.

The pattern terms are programmed by means of signals and logical operators.

Pattern pt0 can be used either as a standard or as a transitional pattern term. Different operators are available for standard and transitional pattern terms.

#### **Using Pattern Terms**

The pattern terms (also known as: pattern recognizers) compare bus states with programmable conditions. Their output (1 = bus pattern found, 0 = bus pattern not found) can be used:

- as input for sequencers, for example, the trace memory trigger sequencer (see "Sequencer Programming" on page 55).

- for storage qualification for the trace memory (see "Trace Memory Programming" on page 70).

- when counting bus events for performance analysis (see "Performance Measurement Programming" on page 64).

- for master conditional start based on the detection of a specific event on the PCI bus (see "*Master Run*" on page 103).

As input, the pattern terms can use all the signals specified in "b\_signaltype (List of Signals)" in the Agilent E2925B Opt. 320 C-API/PPR Reference.

24 pattern terms (named pt0  $\dots$  pt23) are implemented on the testcard. pt0 can be used as input for the trace memory trigger only.

**Types of Pattern Terms**

By default, all pattern terms are standard pattern terms. However, the pattern term pt0 is a special pattern term; it can be switched between standard pattern term and transitional pattern term.

• Standard pattern terms

The standard pattern terms detect the **state** of a signal (either 0 or 1) in contrast to transitional patterns, which detect the change of a signal.

If a standard pattern term queries multiple signals, all signals are combined via logical AND.

To allow an easy trigger on any protocol combination, the pattern recognition of protocol attributes is aligned with the associated data transfer.

• Transitional pattern term

The transitional pattern term detects **state changes** of signals. If it queries multiple signals, all signals are combined via logical OR.

A transitional pattern term can be used for an efficient storage qualification when samples are to be taken only on *changes* of relevant signals.

### **Functions Overview**

**Programming Options**

Programming pattern terms allows the following options:

- To specify a pattern term, use *BestPattSet*.

This pattern term can be used in the condition strings of a sequencer description table.

- To set compare patterns for trace memory control, use BestTracePattPropSet.

## **Example**

**Task** Program the following three pattern terms:

• Detection of transactions on video memory for triggering:

```

pt0 = "b state==3\h && AD32==b8xxx\h''

```

This makes pattern term pt0 sensitive to address phases (b\_state==3\h) and sensitive to signals on the address/data lines in the address space between b8000\h and b8FFF\h.

• Filtering of waits from stored data:

```

pt1 = "b_state==7h"

```

This sets up pattern term pt1 to detect data transfers. Inverted pt1 (!pt1) can then be used to filter waits. This condition should be used as a storage qualifier.

• Detecting the end of a data transfer:

```

pt2 = "b state==1"

```

This makes pattern term pt2 sensitive to idles and thus to the end of the data transfer.

**Implementation**

# **Sequencer Programming**

The sequencers of the testcard detect bus state sequences. The sequencers use programmable pattern terms to compare bus states with programmable conditions.

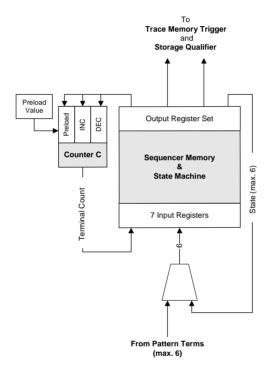

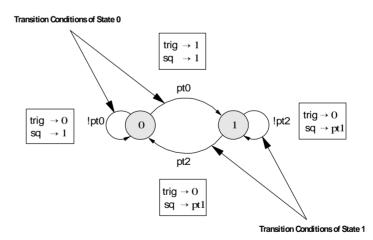

Representive of all sequencers, the figure below shows the trace memory trigger sequencer. The only difference to other sequencers is its output: the trace memory trigger signal and the storage qualifier signal.

All sequencers provide an internal memory and state machine, and a 32-bit feedback counter C. The statemachine controls the operation of the sequencer. The sequencer has 7 input registers. One of the registers is used for the terminal count of the sequencer's own feedback counter. The remaining 6 registers can be used for input from pattern terms and for state feedback from the sequencer output. A maximum of  $2^5$ = 32 states is the practical limit—because at least one pattern term is always needed.

Setting up the Sequencer

Setting up a sequencer requires the following steps:

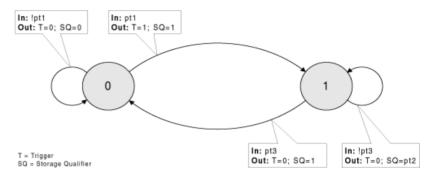

1. Building a state diagram.

A sequence consists of states. The sequencer switches between these states as defined by transition conditions. A state diagram is used to design the sequence.

State diagrams show the transition conditions and the actions to be performed upon transition (output conditions).

#### **Example:**

2. Programming the pattern terms.

This is described in "Programming the Pattern Terms" on page 52.

3. Setting up and programming the sequencer description table.

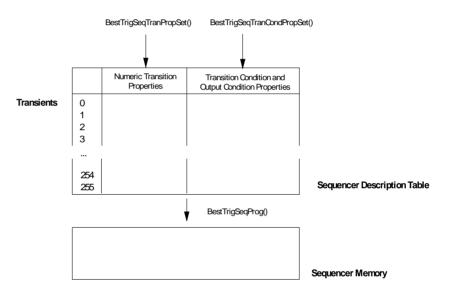

The sequencer description table holds the transients. The transients are programmed using C function calls (or CLI commands). The sequencer description table may contain up to 256 transients.

The state diagram can easily be translated into a sequencer description table. Each transition (arrow) in the diagram requires a transient (a row in the table). Each transient holds the following properties:

- State

State to which the transient is assigned (start of the arrow).

- Next state

State to which the sequencer should change if the transition condition occurs (end of the arrow).

- Transition condition

If this condition is true, the sequencer switches to the "next state".

- Feedback counter enable condition

Output conditions controlling the count operation of the feedback counter (not used in this example).  Feedback counter preload conditions

Output conditions to set the feedback counter to its preload value (not used in this example).

The trace memory trigger sequencer requires in particular:

- Trigger condition

- Output condition controlling the trigger signal. The trigger signal will only be set if this condition is true and if the transient is active.

- Storage qualifier condition

Output condition controlling data sampling (storage qualifier). If this condition is true for a trace data line, this line will be stored to trace memory. Otherwise, timestamp information will be stored at the end of the gap (in normal gap mode).

#### **Example:**

The following table shows an excerpt from a sequencer description table.

| Transient No. | Current State | Next State | Transition<br>Condition | Output<br>Conditions     |

|---------------|---------------|------------|-------------------------|--------------------------|

| 0             | 0             | 0          | !pt0                    | Depends on the sequencer |

| 1             | 0             | 1          | pt0                     |                          |

| 2             | 1             | 1          | !pt2                    |                          |

| 3             | 1             | 0          | pt2                     |                          |

The sequencer starts in state 0. It observes the transition conditions of the current state and performs the actions as defined for an active transition. If no transition condition is true, the sequencer remains in the current state and no action is taken.

- **NOTE** When programming the sequencer description table, note the following behavior of the feedback counter:

- Clock n: The sequencer instructs the counter to decrement.

- Clock n+1: The counter decrements to terminal count.

- Clock n+2: tc input to sequencer is asserted.

There may be additional sequence states and transitions required to get the desired sequencer behavior. See

<install\_dir>\samles\gui\mwi\_not8.cli for an example.

NOTE

If the preload condition occurs simultaneously with an increment/decrement condition, the counter amount will be replaced by the preload value but not incremented or decremented (the preload condition has priority over the count enables).

### **Functions Overview**

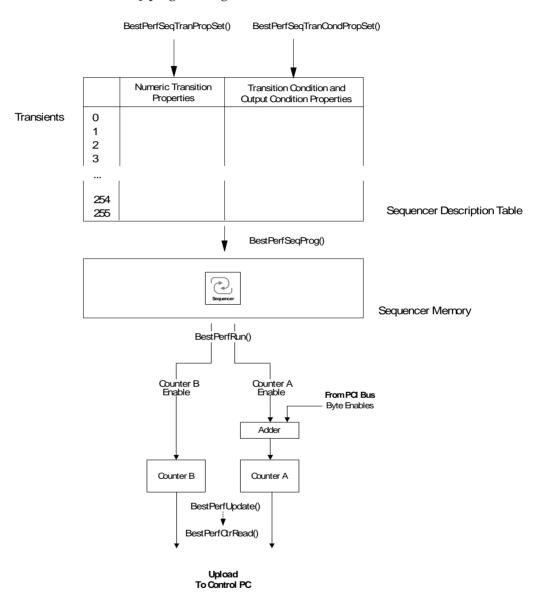

The following figure gives an overview of the sequencer memory programming model (pattern terms and trigger position counter are not considered).

**Programming Steps** Programming the sequencer requires the following steps:

1 Set the preload value of the feedback counter.

${\bf Use}\ {\it BestTrigSeqGenPropSet}.$

**2** Set all properties in the trigger sequencer description table to default values.

Use BestTrigSeqPropDefaultSet.

**3** Set numeric transition properties "Current State" and "Next State".

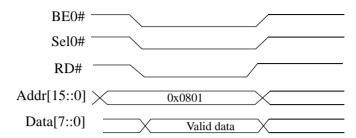

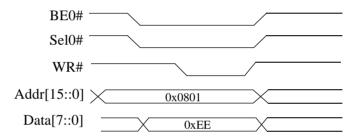

NOTE All transition conditions of one state must be mutual exclusive. This means that one and only one transition condition of a state must turn true at a time. Otherwise, the software will not accept the table because the table does not uniquely define the sequencer's behavior.